# AXIS ETRAX 100LX Designer's Reference

Axis Communications AB cannot be held responsible for any technical or typographical errors, and reserves the right to make changes to this manual and to the product without prior notice. If you do detect any inaccuracies or omissions, please inform us at:

E-mail: technology@axis.com

Axis Communications AB Emdalavägen 14 SE-223 69 Lund, Sweden Phone:+46 46 272 1800 Fax: +46 46 13 61 30

Copyright © Axis Communications AB

| 1 In         | troduction                               | 1  |

|--------------|------------------------------------------|----|

| 1.1          | Overview                                 | 1  |

| 1.2          | Features                                 | 2  |

| 1.3          | Functional Block Diagram                 |    |

| 9 DI         | SC CPU                                   | _  |

|              |                                          |    |

| 2.1 2.2      | Registers  Flogs and Condition Codes     |    |

| 2.3          | Flags and Condition Codes                |    |

|              | Data Organization in Memory              |    |

| 2.4<br>2.4.1 | Instruction Format                       |    |

|              | Addressing Modes                         |    |

| 2.4.2        | Data Transfers                           |    |

| 2.4.3        | Arithmetic Instructions                  |    |

| 2.4.4        | Logical Instructions                     |    |

| 2.4.5        | Shift Instructions                       |    |

| 2.4.6        | Bit Test Instructions                    |    |

| 2.4.7        | Condition Code Manipulation Instructions |    |

| 2.4.8        | Jump and Branch Instructions             |    |

| 2.4.9        | No Operation Instruction                 |    |

| 2.5          | MMU Support                              |    |

| 2.5.1        | Overview                                 |    |

| 2.5.2        | Protected Registers and Flags            |    |

| 2.5.3        | Transition Between Operation Modes       |    |

| 2.5.4        | Bus Fault Sequence                       |    |

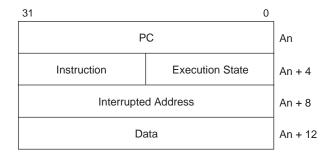

| 2.5.5        | Format of the CPU Status Record          |    |

| 2.6          | Integral Read-Write Operations           |    |

| 2.7          | Interrupts                               |    |

| 2.7.1        | NMI                                      |    |

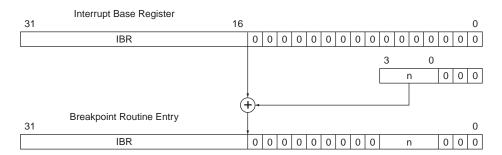

| 2.8          | Software Breakpoints                     |    |

| 2.9          | Hardware Breakpoint Mechanism            | 20 |

| 3 Si         | ngle step                                | 21 |

| 3.1          | General                                  |    |

| 3.2          | Programming Considerations               |    |

|              |                                          |    |

|              | emory Management Unit                    |    |

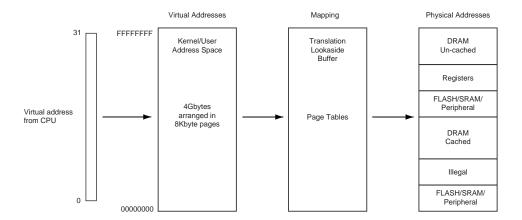

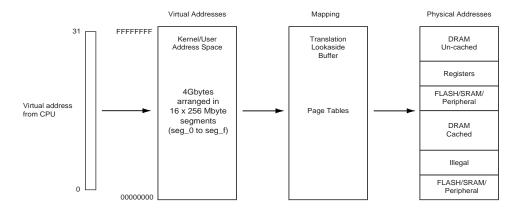

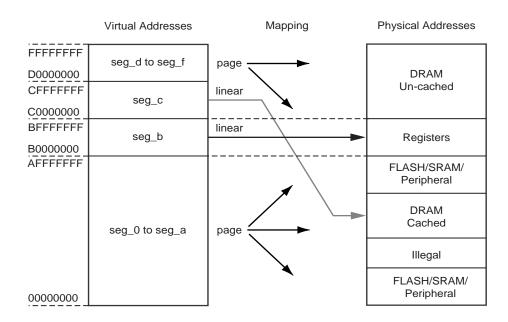

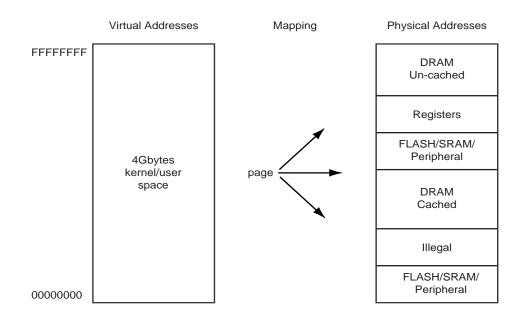

| 4.1          | MMU Memory Areas                         |    |

| 4.1.1        | Kernel/User Address Space                |    |

| 4.1.2        | Kernel Address Space                     |    |

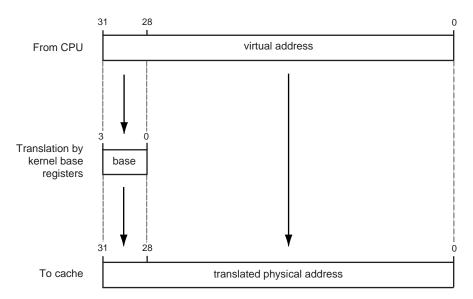

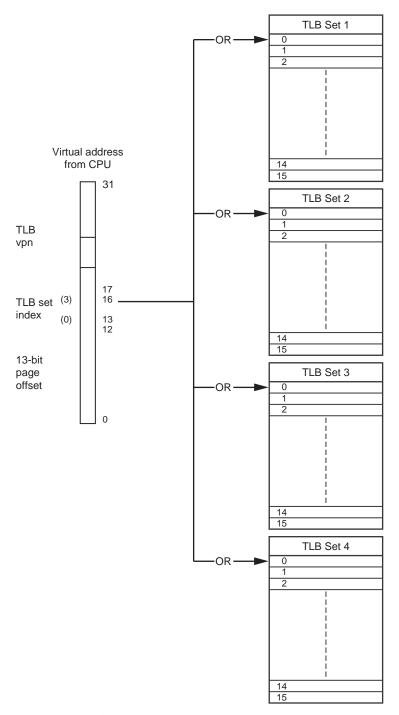

| 4.2          | Translation Lookaside Buffer             |    |

| 4.2.1        | TLB Memory Sets                          |    |

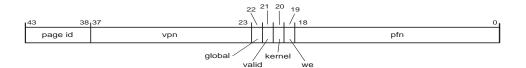

| 4.2.2        | TLB Entries                              |    |

| 4.2.3        | TLB Register Interface                   |    |

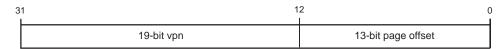

| 4.2.4        | Virtual Address from the CPU             |    |

| 4.2.5        | MMU Exceptions                           |    |

| 4.3          | MMU Registers                            |    |

| 4.4          | MMU Test Mode                            |    |

| 4.5          | Example of Virtual Memory Configuration  | 34 |

| 5 Bu           | ıs Interface                                               | 37          |

|----------------|------------------------------------------------------------|-------------|

| 5.1            | Data Bus                                                   | 37          |

| 5.2            | Bus Interface Registers                                    |             |

| 5.3            | Address and Chip Selects                                   |             |

| 5.4            | Internal Bus Arbitration                                   |             |

| 5.5            | Bus Width, Cycle Timing and Wait States                    |             |

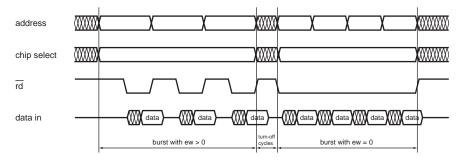

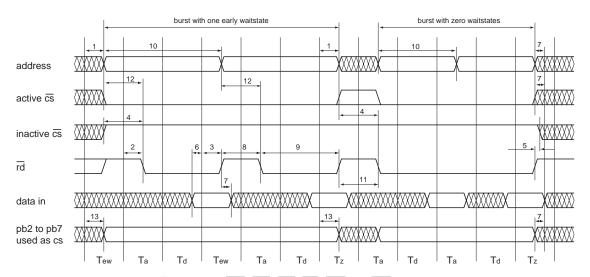

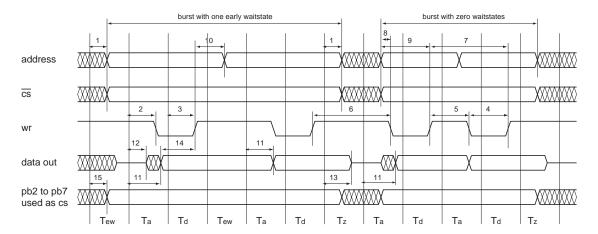

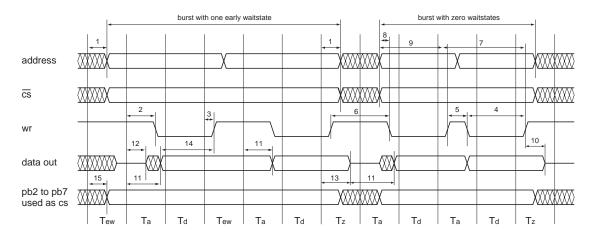

| 5.6            | Memory Timing                                              |             |

| 5.7            | Write Modes                                                |             |

| 5.7.1          | Normal and Extended Write Mode                             |             |

| 5.7.2          | Bytewise and Common Write Enable Mode                      |             |

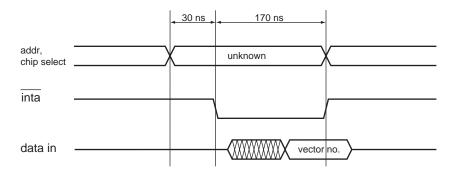

| 5.8            | External Interrupt Acknowledge                             |             |

| 5.9            | Access to Internal I/O                                     |             |

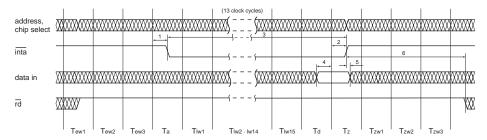

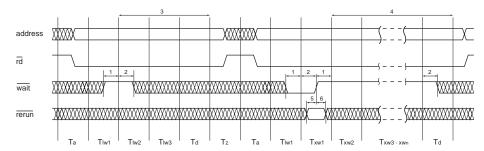

| 5.10           | Wait Input and Bus Cycle Rerun                             |             |

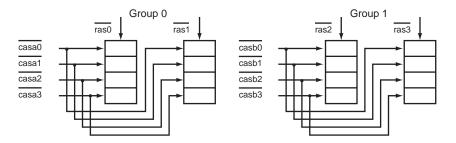

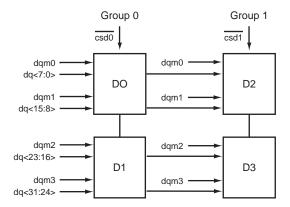

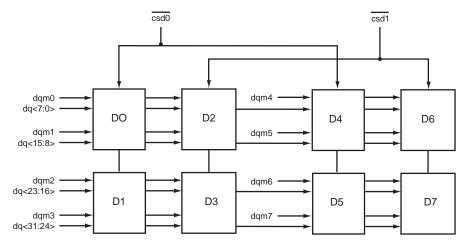

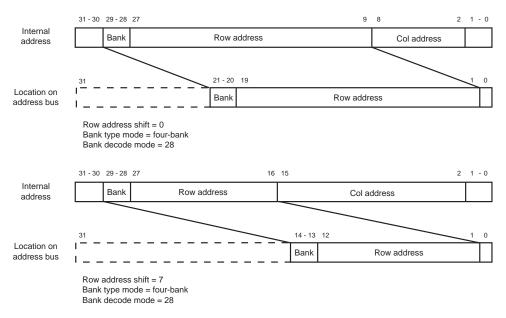

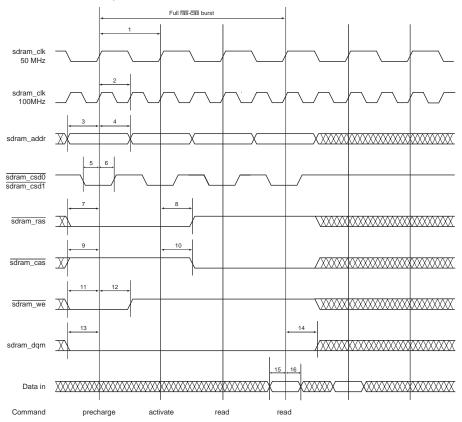

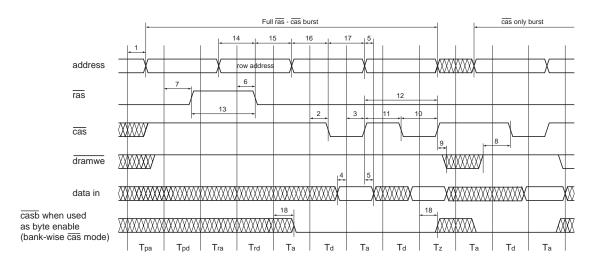

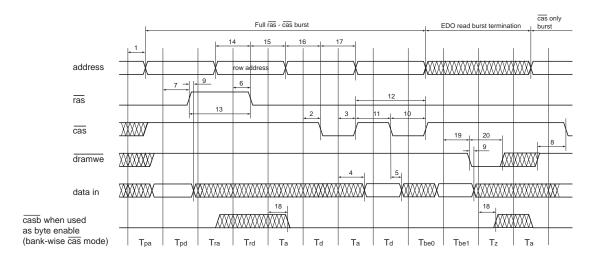

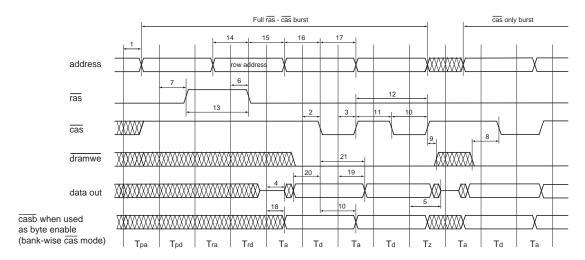

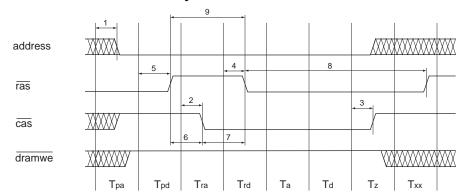

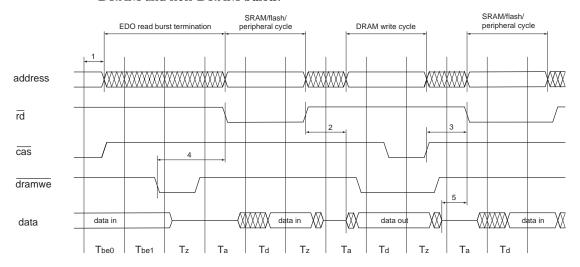

| 5.11           | DRAM Interfaces                                            |             |

| 5.12           | Asynchronous DRAM Interface                                |             |

| 5.12.1         | ·                                                          |             |

| 5.12.2         |                                                            |             |

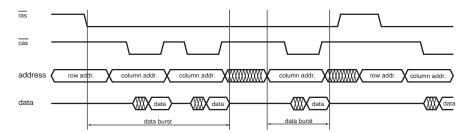

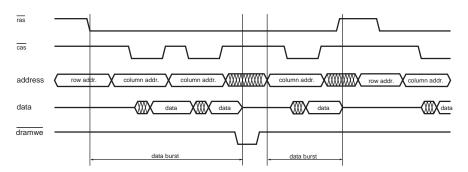

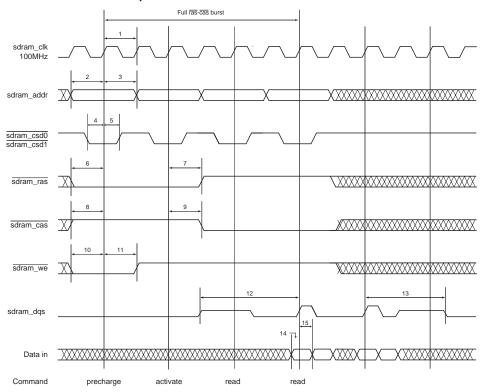

|                | Synchronous DRAM Interface                                 |             |

| 5.13.1         | •                                                          |             |

| 5.13.2         | •                                                          |             |

| 5.13.3         |                                                            |             |

| 5.13.4         |                                                            |             |

| 5.13.5         |                                                            |             |

| 5.13.6         |                                                            |             |

| 6 Bo           | ootstrap Methods                                           | 57          |

| 6.1            | Bootstrap Methods                                          |             |

| 6.1.1          | Normal Bootstrap                                           |             |

| 6.1.2          | Serial Bootstrap                                           |             |

| 6.1.3          | Network Bootstrap                                          |             |

| 6.1.4          | Parallel Bootstrap                                         |             |

| ~ D            | •                                                          |             |

|                | MA                                                         | . <b>59</b> |

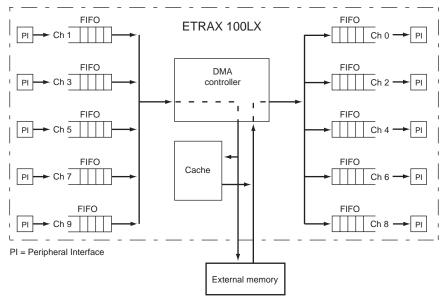

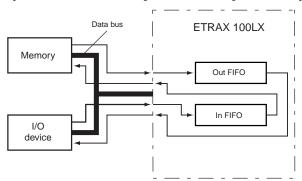

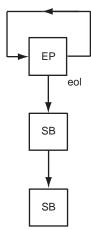

| 7.1            | DMA Operation                                              |             |

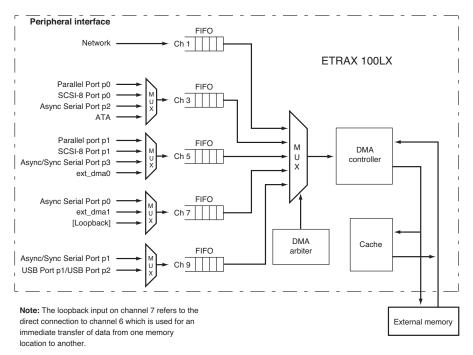

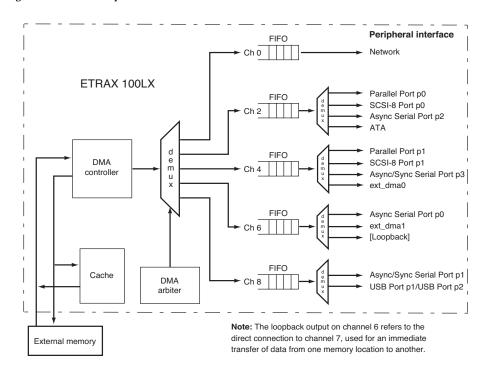

| 7.1.1          | Overview of the ETRAX 100LX DMA Architecture               |             |

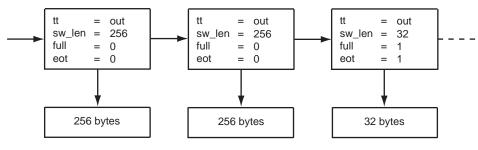

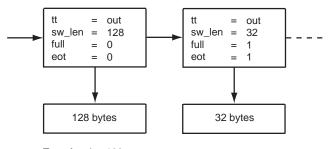

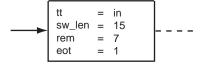

| 7.1.2          | Data Transfer                                              |             |

| 7.2            | The DMA Channels                                           |             |

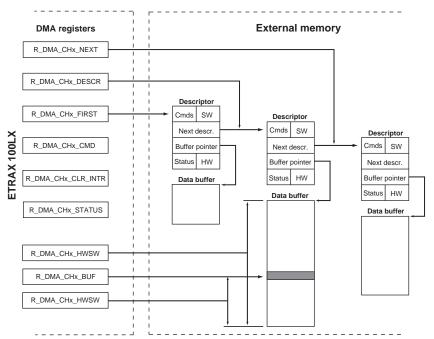

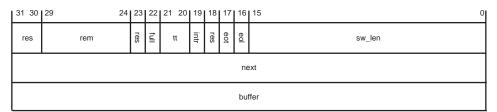

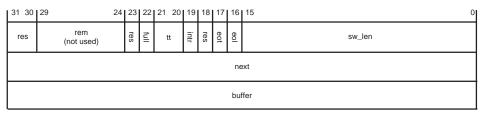

| 7.3            | DMA Registers, Linked Lists, and Descriptor Format         |             |

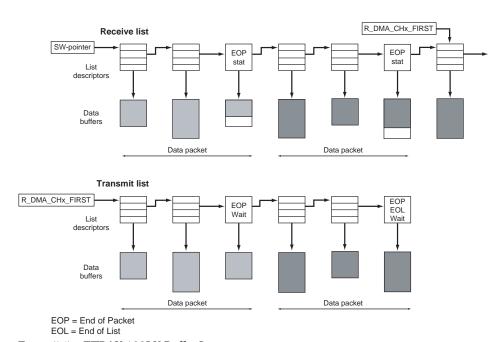

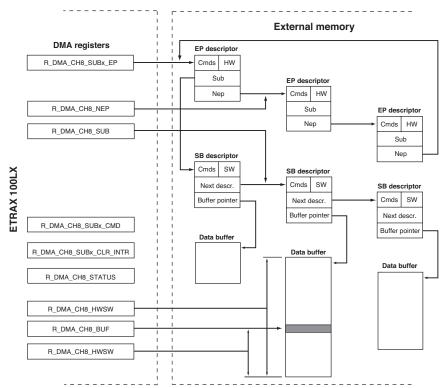

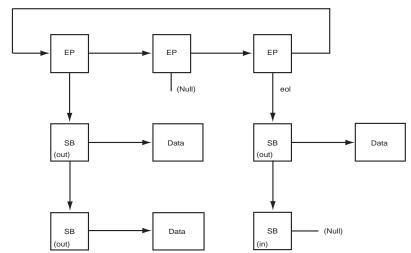

| 7.3.1          | DMA Links Lists                                            |             |

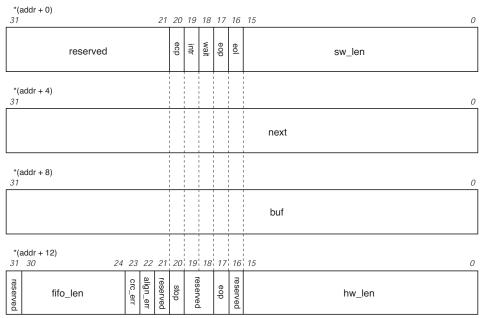

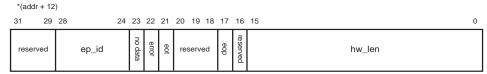

| 7.3.2          | DMA Descriptor Franct                                      |             |

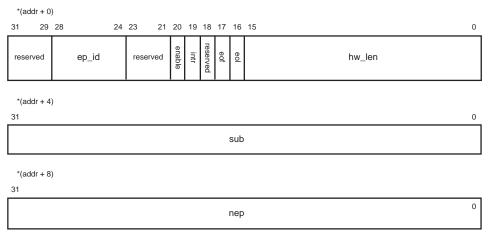

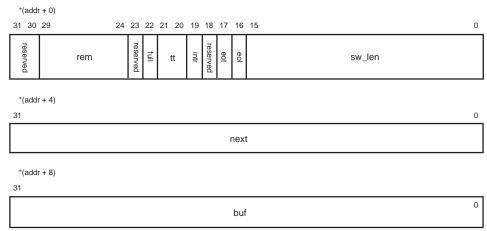

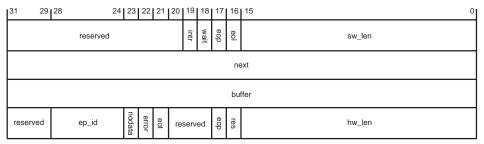

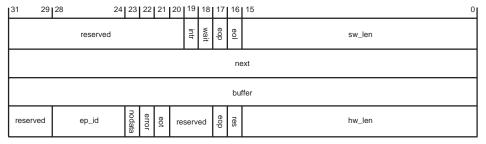

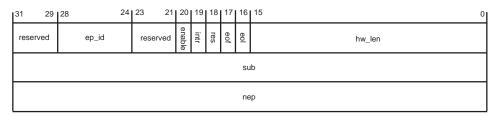

| 7.3.3          | DMA Descriptor Format                                      |             |

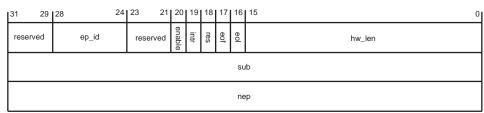

| 7.4            | DMA Registers, Linked Lists, and Descriptor Format for USB |             |

| 7.4.1<br>7.4.2 | DMA Registers for USB  DMA Linked Lists for USB            |             |

| 1 /1 7         | LINIA LINKEA LISIS TOT LINK                                | . 09        |

|                |                                                            |             |

| 7.4.3          | DMA Descriptor Format for USB                              | . 70        |

|                |                                                            | . 70<br>75  |

| 7.6.1 | Initiate and Setup a DMA Transfer           | 76  |

|-------|---------------------------------------------|-----|

| 7.6.2 | Reset DMA Channel                           | 76  |

| 7.6.3 | Initiating Linked List                      | 77  |

| 7.6.4 | Start a DMA Transfer                        | 77  |

| 7.6.5 | Restart a DMA Transfer                      | 77  |

| 7.6.6 | Hold DMA Temporarily and Continue Later     | 78  |

| 7.7   | Memory to Memory DMA                        | 78  |

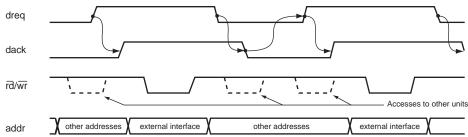

| 7.8   | External DMA Channels                       | 79  |

| 7.8.1 | External DMA Configuration                  | 80  |

| 7.8.2 | External DMA Address                        |     |

| 7.8.3 | Initialization                              | 80  |

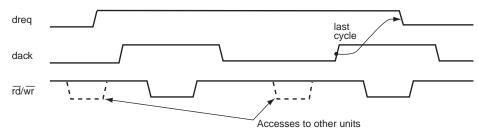

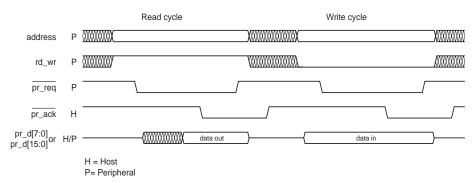

| 7.8.4 | Request/Acknowledge Signaling               | 81  |

| 7.8.5 | Start and Stop of the Transfers             |     |

| 7.8.6 | Transfer Counter                            |     |

| 7.8.7 | External DMA Interrupts                     | 82  |

| 8 U1  | niversal Serial Bus                         | 83  |

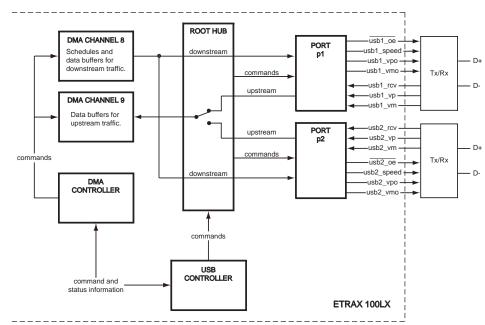

| 8.1   | Principle of Operation                      | 84  |

| 8.1.1 | Basic Architecture of the USB Interface     | 84  |

| 8.1.2 | Modes of Operation of the USB Interface     | 84  |

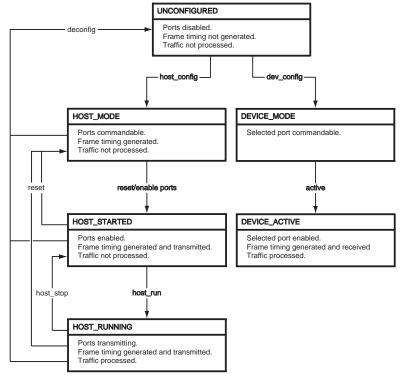

| 8.2   | Operational States of the USB Controller    | 85  |

| 8.3   | USB Registers                               | 86  |

| 8.3.1 | Register Access Timing                      | 86  |

| 8.3.2 | USB Mode Registers                          | 86  |

| 8.4   | USB Host mode                               | 88  |

| 8.4.1 | USB Controller Commands in Host Mode        | 89  |

| 8.4.2 | USB Port (Root Hub) Commands in Host Mode   | 90  |

| 8.5   | USB Data Structures in Host Mode            | 91  |

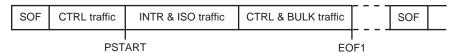

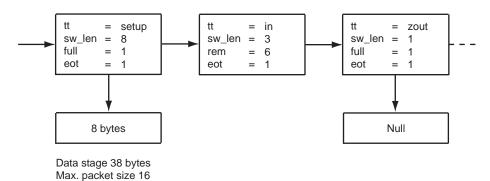

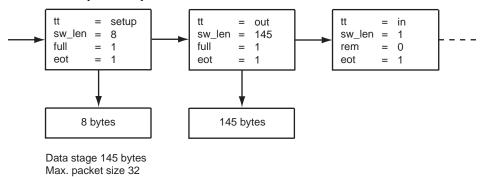

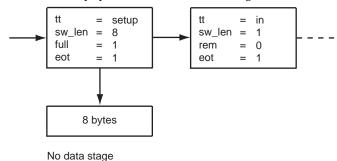

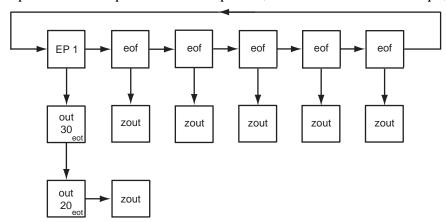

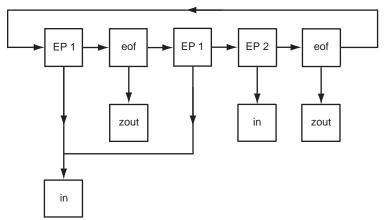

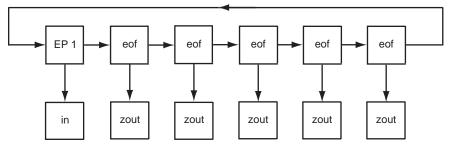

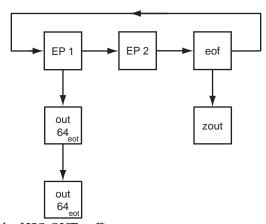

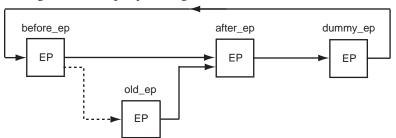

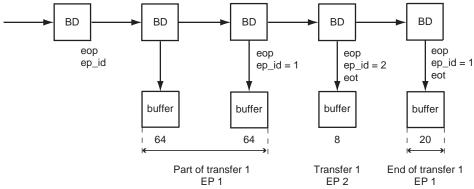

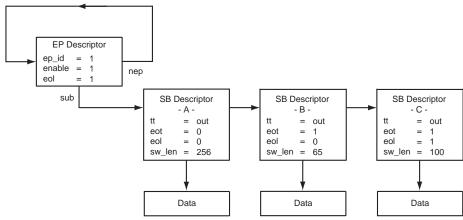

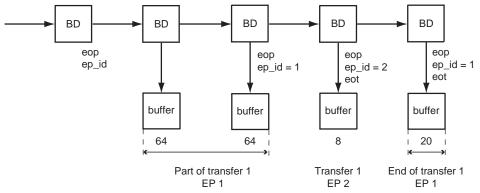

| 8.5.1 | Transfer Frames                             | 91  |

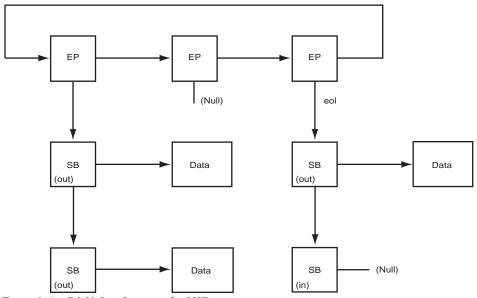

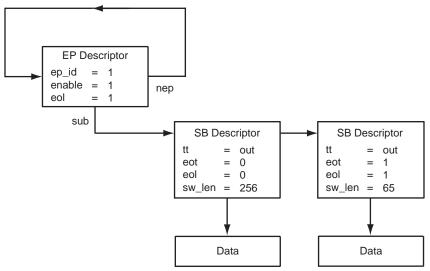

| 8.5.2 | DMA Descriptors                             | 93  |

| 8.5.3 | Endpoint Table in Host Mode                 | 99  |

| 8.5.4 | Host Mode Interrupts                        | 100 |

| 8.6   | Device Mode                                 | 102 |

| 8.6.1 | USB Controller Commands in Device Mode      | 102 |

| 8.6.2 | USB Port (Root Hub) Commands in Device Mode | 103 |

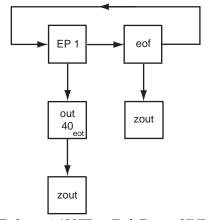

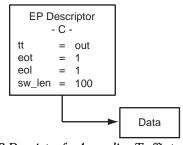

| 8.6.3 | USB Data Structures in Device Mode          | 103 |

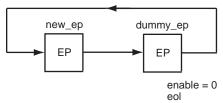

| 8.6.4 | EP Table in Device Mode                     | 105 |

| 8.6.5 | Device Mode Interrupts                      | 106 |

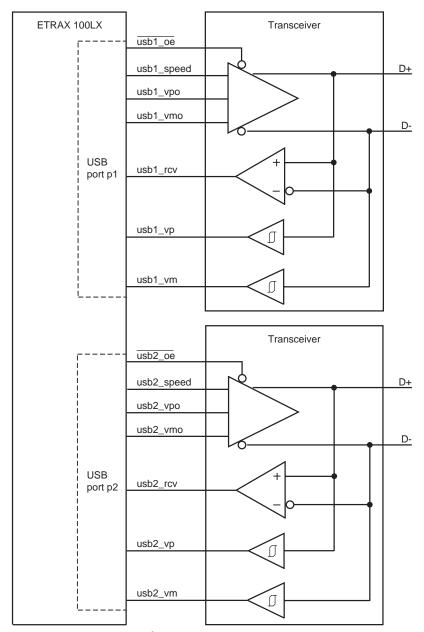

| 8.7   | Physical Interface                          | 107 |

| 8.7.1 | Data Transmission                           | 107 |

| 8.7.2 | Power Management                            | 107 |

| 8.7.3 | Hardware Reset                              |     |

| 8.8   | Procedures                                  |     |

| 8.8.1 | Configuring the USB Interface for Host Mode | 108 |

| 8.8.2 | Starting and Stopping the Host Mode         |     |

| 8.8.3 | Starting and Stopping Traffic in Host Mode  |     |

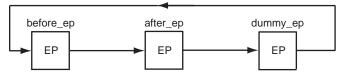

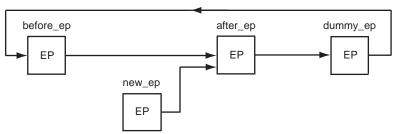

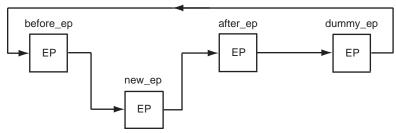

| 8.8.4 | Managing EP Descriptor Lists in Host Mode   | 109 |

| 8.8.5  | Managing SB Descriptor Lists in Host Mode  | 110 |

|--------|--------------------------------------------|-----|

| 8.8.6  | Managing the EP Table in Host Mode         | 111 |

| 8.8.7  | Managing the DMA Channel 9 Descriptor List | 112 |

| 8.8.8  | Managing the Root Hub                      | 112 |

| 8.8.9  | Managing USB IN Traffic in Device Mode     | 113 |

| 8.8.10 |                                            |     |

| 8.8.11 | USB Control Traffic in Device Mode         | 117 |

| 9 Ne   | twork Interface                            | 119 |

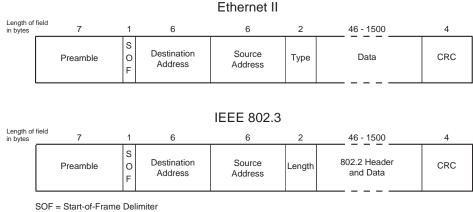

|        | The Ethernet II and IEEE 802.3 Standards   |     |

| 9.2    | Network interface registers                | 120 |

| 9.3    | Network Interface Configuration            | 121 |

|        | Pin Usage in MII and SNI Modes             |     |

| 9.5    | Receiver Logic Functions                   | 122 |

| 9.5.1  | Data Transfer to the Receiving FIFO        | 123 |

| 9.5.2  | Address Recognition                        |     |

| 9.5.3  | Receiver CRC Check.                        | 124 |

| 9.5.4  | Received Frame Length Check                | 124 |

| 9.6    | Transmitter Logic Functions                | 125 |

| 9.6.1  | Transmission of Frames                     | 125 |

| 9.6.2  | CSMA/CD Access Protocol                    | 126 |

| 9.6.3  | Demand Priority Access Protocol            | 126 |

| 9.7    | Management Interface                       | 127 |

| 9.8    | Ethernet Error and Statistics Counters     | 127 |

| 9.9    | Network interrupts                         | 128 |

| 10 EII | DE/ATA-2/ATA-3 Interface                   | 129 |

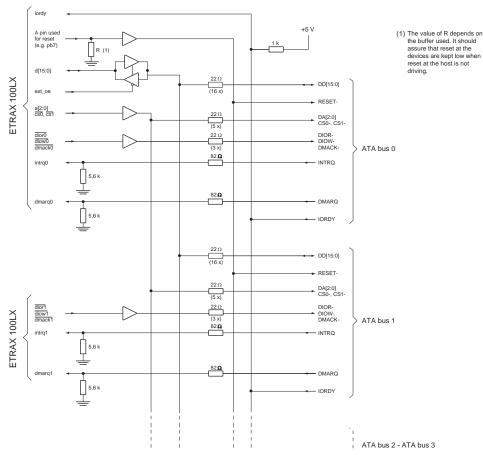

| 10.1   | ATA Interface Pin Connection               | 129 |

| 10.2   | EIDE/ATA-2/ATA-3 Interface Registers       | 130 |

| 10.3   | Data Transfer                              | 130 |

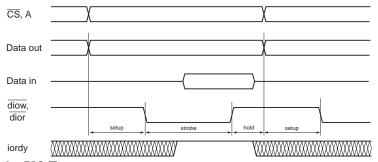

| 10.3.1 | Programmed Input/Output (PIO)              | 130 |

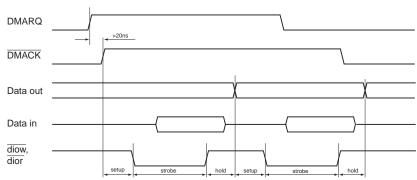

| 10.3.2 | ATA DMA Handshaking                        | 130 |

| 10.3.3 | ETRAX 100LX Register Access                | 131 |

| 10.3.4 | ETRAX 100LX DMA Access                     | 131 |

| 10.4   | Timing                                     | 131 |

| 10.5   | Interrupts                                 | 132 |

| 11 Asy | ynchronous Serial Ports                    | 133 |

|        | General                                    |     |

| 11.2   | Connection to Input/Output Pins            | 133 |

| 11.3   | Asynchronous Serial Port Registers         | 134 |

| 11.4   | Operation Modes                            | 135 |

| 11.5   | Baud Rate Selection                        | 136 |

| 11.6   | CPU Controlled Operation                   | 137 |

| 11.7   | DMA Controlled Operation                   | 137 |

| 11.8   | Asynchronous Serial Port Interrupts        | 138 |

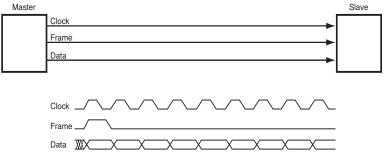

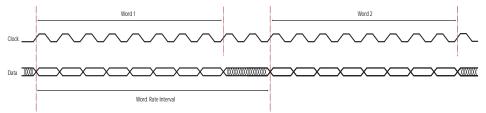

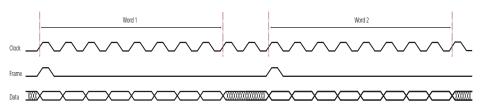

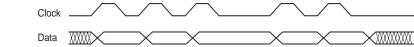

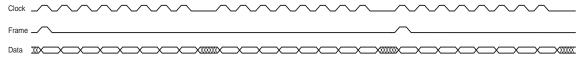

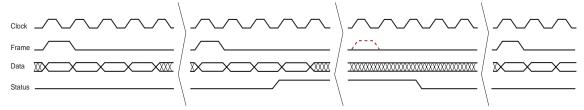

| 12 Syı | nchronous Serial Interface                 | 139 |

| 12.1   | Overview                                         | 139   |

|--------|--------------------------------------------------|-------|

| 12.2   | Mode Selection                                   | 139   |

| 12.3   | Pin Usage                                        | 140   |

| 12.3.1 | l Pin Configuration                              | . 140 |

| 12.3.2 | Pin Usage in the Different Modes                 | . 140 |

| 12.4   | Synchronous Serial Port Registers                |       |

| 12.5   | Configuration                                    |       |

| 12.6   | Word Length                                      |       |

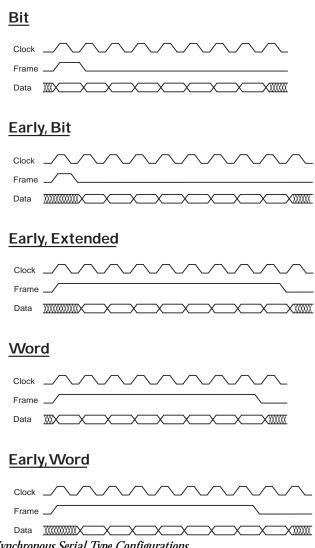

| 12.7   | Frame Synchronization                            | 145   |

| 12.7.1 | Frame Synchronization Modes                      | . 145 |

| 12.7.2 | Prame Strobe Generation                          | . 146 |

| 12.7.3 | 3 Stream Mode                                    | . 146 |

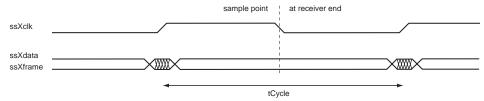

| 12.8   | Clocking                                         | 147   |

| 12.8.1 | l Clock Generator                                | . 147 |

| 12.8.2 | Pata Sampling                                    | . 147 |

| 12.8.3 | 3 Clock Gating                                   | . 148 |

| 12.9   | Flow Control                                     | 149   |

| 12.10  | Interrupts                                       | 149   |

| 12.11  | Using The Sync Serial Ports with DMA             | 150   |

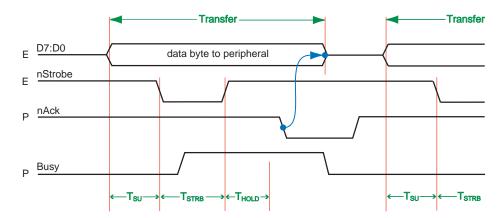

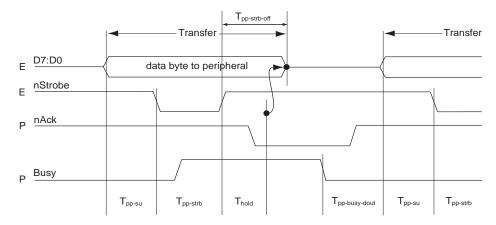

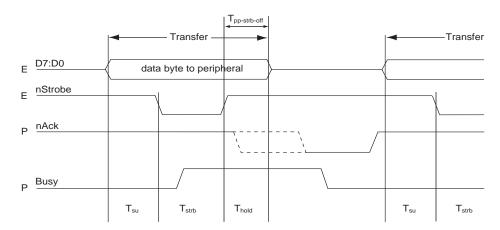

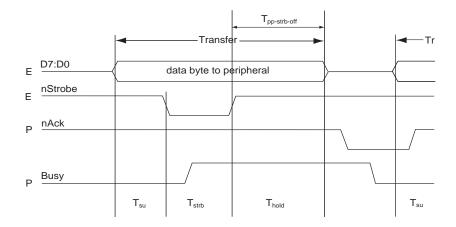

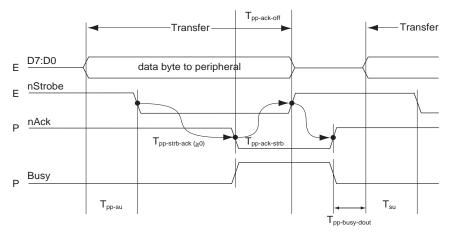

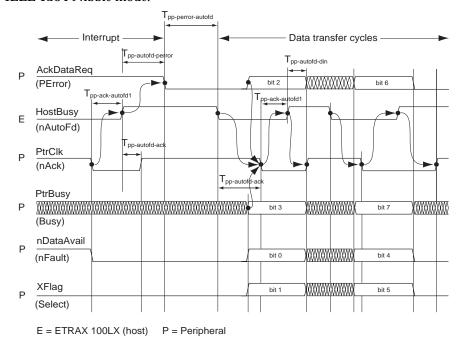

| 13 Pa  | ırallel Ports                                    | 151   |

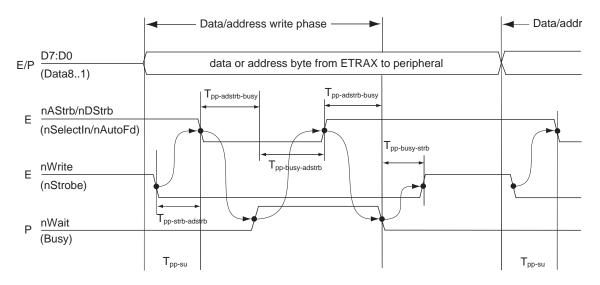

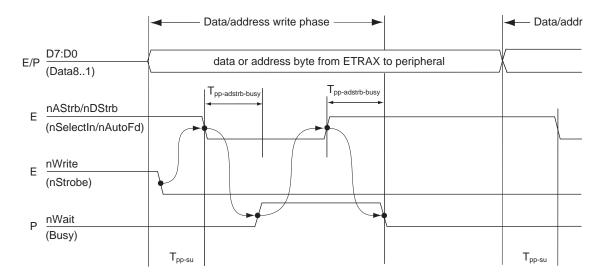

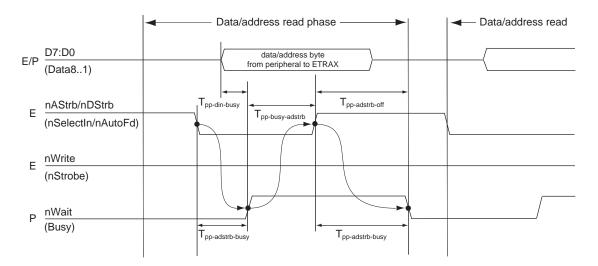

|        | Parallel Port Registers                          |       |

|        | Modes of Operation                               |       |

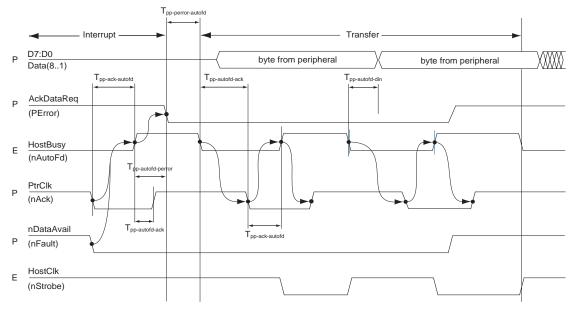

| 13.2.1 | •                                                |       |

| 13.2.2 |                                                  |       |

| 13.2.3 | ,                                                |       |

| 13.2.4 | 4 IEEE-1284 Byte Mode                            | . 159 |

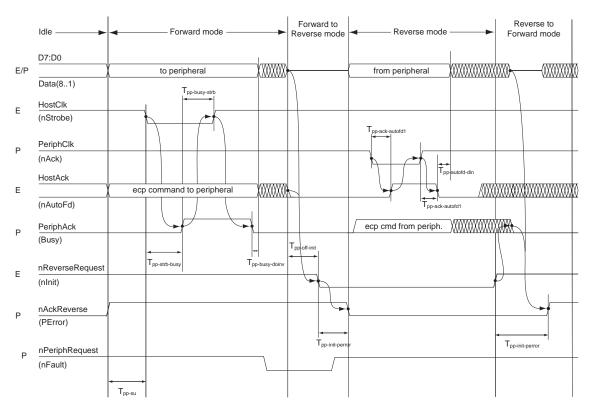

| 13.2.5 | ·                                                |       |

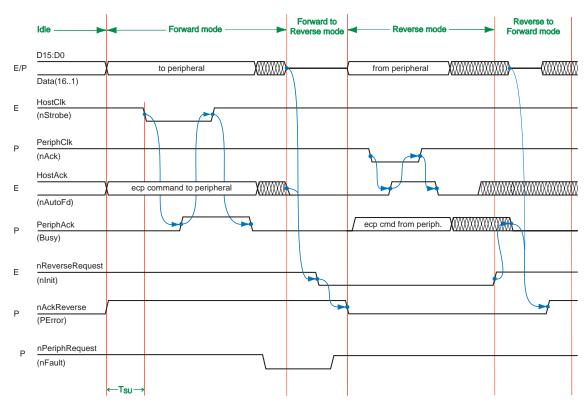

| 13.2.6 | B ECP Wide (16-Bit) Mode                         | . 163 |

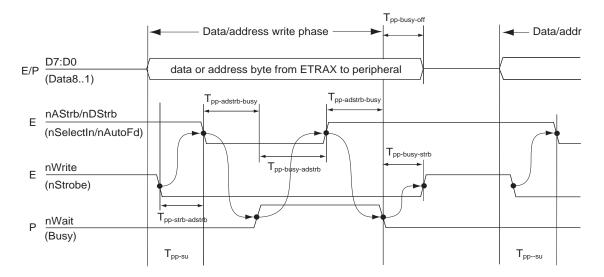

| 13.2.7 | 7 EPP Mode                                       | . 165 |

| 13.2.8 | B Manual Mode                                    | . 169 |

| 13.3   | Parallel Port Interrupts                         | 170   |

| 13.3.1 | Peripheral Interrupt                             | . 170 |

| 13.3.2 | 2 ECP Command Interrupt                          | . 170 |

| 13.3.3 | B Data Available Interrupt                       | . 170 |

| 13.3.4 | 4 Ready Interrupt                                | . 171 |

| 13.3.5 | EPP Interrupts                                   | . 171 |

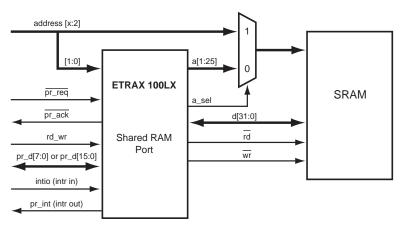

| 14 Sh  | nared RAM Interface                              | 173   |

|        | Shared RAM Interface Configuration               |       |

|        | Shared RAM Interrupts                            |       |

| 15 Ti  | mers                                             | 175   |

| 15.1   | General                                          |       |

| 15.2   | Timer Registers                                  |       |

|        | Clock Prescaling: The Programmable Clock Divider |       |

|        | Programmable Timers.                             |       |

| 15.4.1 | <b>8</b>                                         |       |

## **Contents**

| 15.5 Timer Input Clock                                          | 177 |

|-----------------------------------------------------------------|-----|

| 15.5.1 Timer0 Input Clock                                       | 177 |

| 15.5.2 Timer1 Input Clock                                       | 178 |

| 15.6 Cascade Mode                                               | 178 |

| 15.7 Watchdog Timer                                             | 178 |

| 15.8 Timer Interrupts                                           | 179 |

| 16 General I/O Ports                                            | 181 |

| 16.1 General Port PA                                            |     |

| 16.1.1 Interrupts at General Port PA                            | 181 |

| 16.2 General Port PB                                            |     |

| 16.2.1 Configuration of Signal Directions at General Port PB    | 183 |

| 16.2.2 General Port PB and the I2C Interface                    |     |

| 16.2.3 General Port PB and the Peripheral Chip-Select Signals   |     |

| 16.2.4 General Port PB and the Synchronous Serial Ports         |     |

| 16.2.5 General Port PB and the SCSI Ports                       |     |

| 16.2.6 General Port PB and the USB Ports                        | 185 |

| 16.3 Discrete General Ports                                     |     |

| 16.4 General I/O Registers                                      | 186 |

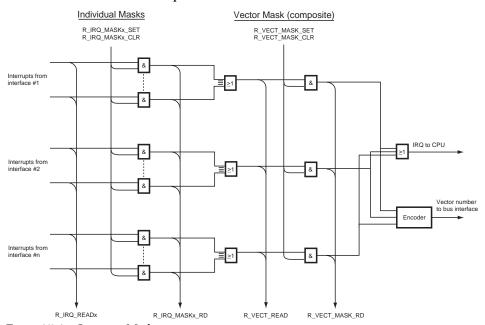

| 17 Interrupts                                                   | 187 |

| 17.1 Interrupt Masks                                            |     |

| 17.2 Interrupt Status                                           |     |

| 17.3 USB Interrupts                                             |     |

| 17.4 Interrupt Registers                                        |     |

| 17.5 Non-Maskable Interrupts                                    |     |

| 17.6 Masked Interrupts with Internally Generated Vector Numbers |     |

| 17.6.1 Interrupts in Register Sub-Set 0                         |     |

| 17.6.2 Interrupts in Register Sub-Set 1                         |     |

| 17.6.3 Interrupts in Register Sub-Set 2                         |     |

| 17.6.4 Interrupts in the USB Register Set                       | 201 |

| 17.6.5 Vector Number Register Sub-Set                           | 202 |

| 17.7 External Maskable Interrupt with an External Vector Number | 204 |

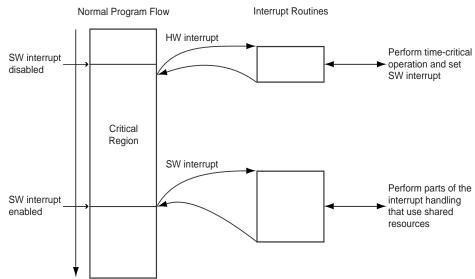

| 17.8 Software Interrupts                                        | 204 |

| 18 Internal Registers                                           | 207 |

| 18.1 Conventions                                                |     |

| 18.1.1 Notation                                                 | 207 |

| 18.1.2 Base Address                                             | 207 |

| 18.2 Bus Interface Configuration Registers                      | 207 |

| 18.2.1 R_WAITSTATES                                             | 207 |

| 18.2.2 R_BUS_CONFIG                                             | 209 |

| 18.2.3 R_BUS_STATUS                                             | 210 |

| 18.2.4 R_DRAM_TIMING                                            | 211 |

| 18.2.5 R_SDRAM_TIMING                                           | 212 |

| 18.2.6 R_DRAM_CONFIG                                            | 213 |

| 18.2.7 R_SDRAM_CONFIG                                           | 215 |

| 18.3 External DMA Registers                                     | 217 |

| 18.3.1  | R_EXT_DMA_0_CMD                     | 217 |

|---------|-------------------------------------|-----|

| 18.3.2  | R_EXT_DMA_0_STAT                    | 218 |

| 18.3.3  | R_EXT_DMA_0_ADDR                    | 219 |

| 18.3.4  | R_EXT_DMA_I_CMD                     | 220 |

| 18.3.5  | R_EXT_DMA_I_STAT                    | 221 |

| 18.3.6  | R_EXT_DMA_I_ADDR                    | 222 |

| 18.4 Ti | mer Registers                       | 223 |

| 18.4.1  | R_TIMER_CTRL                        |     |

| 18.4.2  | R TIMER DATA                        |     |

| 18.4.3  | R TIMER01 DATA                      | 226 |

| 18.4.4  | R_TIMERO_DATA                       | 227 |

| 18.4.5  | R_TIMER1_DATA                       |     |

| 18.4.6  | R WATCHDOG                          |     |

| 18.4.7  | R_CLOCK_PRESCALE                    |     |

| 18.4.8  | R_TIMER_PRESCALE                    |     |

| 18.4.9  | R PRESCALE STATUS                   |     |

| 18.4.10 | R_TIM_PRESC_STATUS                  |     |

|         | ared RAM Interface Registers        |     |

| 18.5.1  | R SHARED RAM CONFIG                 |     |

| 18.5.2  | R_SHARED_RAM_ADDR                   |     |

|         | eneral Configuration Registers      |     |

| 18.6.1  | R GEN CONFIG                        |     |

| 18.6.2  | R_GEN_CONFIG_II                     |     |

| 18.6.3  | R_PORT_G_DATA                       |     |

| 18.7 Ge | eneral Port Configuration Registers |     |

| 18.7.1  | R_PORT_PA_SET                       |     |

| 18.7.2  | R_PORT_PA_DATA                      |     |

| 18.7.3  | R PORT PA DIR                       |     |

| 18.7.4  | R PORT PA READ                      |     |

| 18.7.5  | R_PORT_PB_SET                       |     |

| 18.7.6  | R_PORT_PB_DATA                      |     |

| 18.7.7  | R PORT PB DIR                       |     |

| 18.7.8  |                                     |     |

| 18.7.9  | R_PORT_PB_I2C                       |     |

| 18.7.10 | R_PORT_PB_READ                      |     |

|         | rial Port Registers                 |     |

| 18.8.1  | R SERIALO CTRL                      |     |

| 18.8.2  | R_SERIALO_BAUD                      |     |

| 18.8.3  | R_SERIALO_REC_CTRL                  |     |

| 18.8.4  | R_SERIALO_TR_CTRL                   |     |

| 18.8.5  | R_SERIALO_TR_DATA                   |     |

| 18.8.6  | R_SERIALO_READ                      |     |

| 18.8.7  | R SERIALO STATUS                    |     |

| 18.8.8  | R_SERIALO_REC_DATA                  |     |

| 18.8.9  | R_SERIALO_XOFF                      |     |

| 18.8.10 |                                     |     |

|         |                                     |     |

| 18.8.11 | R_SERIAL1_BAUD             | 263 |

|---------|----------------------------|-----|

| 18.8.12 | R_SERIAL1_REC_CTRL         | 264 |

| 18.8.13 | R_SERIAL1_TR_CTRL          | 265 |

| 18.8.14 | R_SERIAL1_TR_DATA          | 266 |

| 18.8.15 | R_SERIAL1_READ             | 267 |

| 18.8.16 | R_SERIAL1_STATUS           | 268 |

| 18.8.17 | R_SERIAL1_REC_DATA         | 269 |

| 18.8.18 | R_SERIAL1_XOFF             | 270 |

| 18.8.19 | R_SERIAL2_CTRL             | 271 |

| 18.8.20 | R_SERIAL2_BAUD             | 273 |

| 18.8.21 | R_SERIAL2_REC_CTRL         | 274 |

| 18.8.22 | R_SERIAL2_TR_CTRL          | 275 |

| 18.8.23 | R_SERIAL2_TR_DATA          | 276 |

| 18.8.24 | R SERIAL2 READ             |     |

| 18.8.25 | R_SERIAL2_STATUS           | 278 |

| 18.8.26 | R SERIAL2 REC DATA         |     |

| 18.8.27 | R SERIAL2 XOFF             |     |

| 18.8.28 | R_SERIAL3_CTRL             |     |

| 18.8.29 | R_SERIAL3_BAUD             |     |

| 18.8.30 | R_SERIAL3_REC_CTRL         |     |

| 18.8.31 | R_SERIAL3_TR_CTRL          |     |

| 18.8.32 | R_SERIAL3_TR_DATA          |     |

| 18.8.33 | R SERIAL3 READ             |     |

| 18.8.34 | R_SERIAL3_STATUS           |     |

| 18.8.35 | R_SERIAL3_REC_DATA         |     |

| 18.8.36 | R_SERIAL3_XOFF             |     |

|         | R_ALT_SER_BAUDRATE         |     |

| 18.8.38 | R_SERIAL_PRESCALE          |     |

| 18.8.39 | R_SER_PRESC_STATUS         |     |

|         | etwork Interface Registers |     |

| 18.9.1  | R_NETWORK_SA_0             |     |

| 18.9.2  | R_NETWORK_SA_1             |     |

| 18.9.3  | R_NETWORK_SA_2             |     |

| 18.9.4  | R_NETWORK_GA_0             |     |

| 18.9.5  | R_NETWORK_GA_1             |     |

| 18.9.6  | R_NETWORK_REC_CONFIG       |     |

| 18.9.7  | R_NETWORK_GEN_CONFIG       |     |

| 18.9.8  | R_NETWORK_TR_CTRL          |     |

| 18.9.9  | R_NETWORK_MGM_CTRL         |     |

|         | R_NETWORK_STAT             |     |

|         | R_REC_COUNTERS             |     |

|         | R_TR_COUNTERS              |     |

|         | R_PHY_COUNTERS             |     |

|         | rallel Port Registers      |     |

|         | R_PARO_CTRL_DATA           |     |

|         | R_PARO_CTRL                |     |

| 10.10.2 | N_I ANU_C1NL               | 510 |

| 18.10.3  | R_PAR0_STATUS_DATA               | 311 |

|----------|----------------------------------|-----|

|          | R_PAR0_STATUS                    |     |

|          | R PAR ECP16 DATA                 |     |

|          | R PARO CONFIG                    |     |

|          | R_PAR0_DELAY                     |     |

|          | R_PAR1_CTRL_DATA                 |     |

|          | R PAR1 CTRL                      |     |

|          | R_PAR1_STATUS_DATA               |     |

|          | R PAR1 STATUS                    |     |

| 18.10.12 | R PAR1 CONFIG                    | 327 |

|          | R_PAR1_DELAY                     |     |

|          | <br>'A Interface Registers       |     |

|          | R_ATA_CTRL_DATA                  |     |

|          | R_ATA_STATUS_DATA                |     |

|          | R_ATA_CONFIG                     |     |

|          | R_ATA_TRANSFER_CNT               |     |

|          | SI Registers.                    |     |

|          | R_SCSI0_CTRL                     |     |

|          | R SCSIO CMD DATA                 |     |

|          | R_SCSI0_DATA                     |     |

|          | R SCSIO CMD                      |     |

|          | R SCSIO STATUS CTRL              |     |

|          | R_SCSI0_STATUS                   |     |

|          | R_SCSI0_DATA_IN                  |     |

|          | R SCSI1 CTRL                     |     |

|          | R_SCSI1_CMD_DATA                 |     |

|          | R_SCSI1_DATA                     |     |

|          | R SCSI1 CMD                      |     |

|          | R_SCSI1_STATUS_CTRL              |     |

|          | R_SCSI1_STATUS                   |     |

|          | R_SCSI1_DATA_IN                  |     |

|          | errupt Mask and Status Registers |     |

|          | R_IRQ_MASK0_RD                   |     |

|          | R_IRQ_MASK0_CLR                  |     |

|          | R_IRQ_READ0                      |     |

|          | R_IRQ_MASK0_SET                  |     |

|          | R IRQ MASK1 RD                   |     |

|          | R_IRQ_MASK1_CLR                  |     |

|          | R_IRQ_READ1                      |     |

|          | R_IRQ_MASK1_SET                  |     |

|          | R_IRQ_MASK2_RD                   |     |

|          | R_IRQ_MASK2_CLR                  |     |

|          | R_IRQ_READ2                      |     |

|          | R_IRQ_MASK2_SET                  |     |

|          | R_VECT_MASK_RD                   |     |

|          | R_VECT_MASK_CLR                  |     |

| 10.10.14 |                                  | 500 |

| 18.13.15 R_VECT_READ        | 388 |

|-----------------------------|-----|

| 18.13.16 R_VECT_MASK_SET    | 390 |

| 18.14 DMA Registers         | 391 |

| 18.14.1 R_SET_EOP           | 391 |

| 18.14.2 R_DMA_CH0_HWSW      | 392 |

| 18.14.3 R_DMA_CH0_DESCR     | 393 |

| 18.14.4 R_DMA_CH0_NEXT      | 394 |

| 18.14.5 R_DMA_CH0_BUF       | 395 |

| 18.14.6 R_DMA_CH0_FIRST     | 396 |

| 18.14.7 R_DMA_CH0_CMD       | 397 |

| 18.14.8 R_DMA_CH0_CLR_INTR  | 398 |

| 18.14.9 R_DMA_CH0_STATUS    | 399 |

| 18.14.10 R_DMA_CH1_HWSW     | 400 |

| 18.14.11 R_DMA_CH1_DESCR    | 401 |

| 18.14.12 R_DMA_CH1_NEXT     | 402 |

| 18.14.13 R DMA CH1 BUF      | 403 |

| 18.14.14 R_DMA_CH1_FIRST    | 404 |

| 18.14.15 R DMA CH1 CMD      |     |

| 18.14.16 R DMA CH1 CLR INTR | 406 |

| 18.14.17 R_DMA_CH1_STATUS   |     |

| 18.14.18 R_DMA_CH2_HWSW     |     |

| 18.14.19 R DMA CH2 DESCR    |     |

| 18.14.20 R_DMA_CH2_NEXT     |     |

| 18.14.21 R_DMA_CH2_BUF      |     |

| 18.14.22 R_DMA_CH2_FIRST    |     |

| 18.14.23 R_DMA_CH2_CMD      |     |

| 18.14.24 R_DMA_CH2_CLR_INTR |     |

| 18.14.25 R_DMA_CH2_STATUS   |     |

| 18.14.26 R_DMA_CH3_HWSW     |     |

| 18.14.27 R_DMA_CH3_DESCR    |     |

| 18.14.28 R_DMA_CH3_NEXT     |     |

| 18.14.29 R_DMA_CH3_BUF      |     |

| 18.14.30 R_DMA_CH3_FIRST    |     |

| 18.14.31 R_DMA_CH3_CMD      |     |

| 18.14.32 R DMA CH3 CLR INTR |     |

| 18.14.33 R_DMA_CH3_STATUS   |     |

| 18.14.34 R_DMA_CH4_HWSW     |     |

| 18.14.35 R_DMA_CH4_DESCR    |     |

| 18.14.36 R_DMA_CH4_DESCR    |     |

| 18.14.37 R_DMA_CH4_BUF      |     |

| 18.14.37 R_DMA_CH4_BUF      |     |

| 18.14.39 R_DMA_CH4_FIRS1    |     |

|                             |     |

| 18.14.40 R_DMA_CH4_CLR_INTR |     |

| 18.14.41 R_DMA_CH4_STATUS   |     |

| 18.14.42 R_DMA_CH5_HWSW     |     |

| 18.14.43 R_DMA_CH5_DESCR    | 433 |

| 18.14.44 R_DMA_CH5_NEXT          | 434 |

|----------------------------------|-----|

| 18.14.45 R_DMA_CH5_BUF           | 435 |

| 18.14.46 R_DMA_CH5_FIRST         | 436 |

| 18.14.47 R_DMA_CH5_CMD           | 437 |

| 18.14.48 R_DMA_CH5_CLR_INTR      | 438 |

| 18.14.49 R_DMA_CH5_STATUS        | 439 |

| 18.14.50 R_DMA_CH6_HWSW          | 440 |

| 18.14.51 R_DMA_CH6_DESCR         | 441 |

| 18.14.52 R_DMA_CH6_NEXT          | 442 |

| 18.14.53 R_DMA_CH6_BUF           | 443 |

| 18.14.54 R_DMA_CH6_FIRST         | 444 |

| 18.14.55 R_DMA_CH6_CMD           | 445 |

| 18.14.56 R_DMA_CH6_CLR_INTR      | 446 |

| 18.14.57 R_DMA_CH6_STATUS        | 447 |

| 18.14.58 R_DMA_CH7_HWSW          | 448 |

| 18.14.59 R_DMA_CH7_DESCR         | 449 |

| 18.14.60 R_DMA_CH7_NEXT          | 450 |

| 18.14.61 R_DMA_CH7_BUF           | 451 |

| 18.14.62 R_DMA_CH7_FIRST         | 452 |

| 18.14.63 R_DMA_CH7_CMD           | 453 |

| 18.14.64 R_DMA_CH7_CLR_INTR      | 454 |

| 18.14.65 R_DMA_CH7_STATUS        | 455 |

| 18.14.66 R_DMA_CH8_HWSW          | 456 |

| 18.14.67 R_DMA_CH8_DESCR         | 457 |

| 18.14.68 R_DMA_CH8_NEXT          | 458 |

| 18.14.69 R_DMA_CH8_BUF           | 459 |

| 18.14.70 R_DMA_CH8_FIRST         | 460 |

| 18.14.71 R_DMA_CH8_CMD           | 461 |

| 18.14.72 R_DMA_CH8_CLR_INTR      | 462 |

| 18.14.73 R_DMA_CH8_STATUS        | 463 |

| 18.14.74 R_DMA_CH8_SUB           | 464 |

| 18.14.75 R_DMA_CH8_NEP           | 465 |

| 18.14.76 R_DMA_CH8_SUB0_EP       | 466 |

| 18.14.77 R_DMA_CH8_SUB0_CMD      | 467 |

| 18.14.78 R_DMA_CH8_SUB0_CLR_INTR | 468 |

| 18.14.79 R_DMA_CH8_SUB1_EP       | 469 |

| 18.14.80 R_DMA_CH8_SUB1_CMD      | 470 |

| 18.14.81 R_DMA_CH8_SUB1_CLR_INTR | 471 |

| 18.14.82 R_DMA_CH8_SUB2_EP       | 472 |

| 18.14.83 R_DMA_CH8_SUB2_CMD      | 473 |

| 18.14.84 R_DMA_CH8_SUB2_CLR_INTR | 474 |

| 18.14.85 R_DMA_CH8_SUB3_EP       | 475 |

| 18.14.86 R_DMA_CH8_SUB3_CMD      |     |

| 18.14.87 R_DMA_CH8_SUB3_CLR_INTR |     |

| 18.14.88 R_DMA_CH9_HWSW          | 478 |

| 18.14.89 R_DMA_CH9_DESCR         |     |

| 18.14.90 | R_DMA_CH9_NEXT                                  | 480 |

|----------|-------------------------------------------------|-----|

| 18.14.91 | R_DMA_CH9_BUF                                   | 481 |

| 18.14.92 | R_DMA_CH9_FIRST                                 | 482 |

| 18.14.93 | R_DMA_CH9_CMD                                   | 483 |

| 18.14.94 | R_DMA_CH9_CLR_INTR                              | 484 |

| 18.14.95 | R_DMA_CH9_STATUS                                | 485 |

|          | st Mode Registers                               |     |

| 18.15.1  | R_TEST_MODE                                     | 486 |

| 18.15.2  | R_SINGLE_STEP                                   | 488 |

| 18.16 Un | uiversal Serial Bus Interface Control Registers | 489 |

|          | R_USB_REVISION                                  |     |

| 18.16.2  | R_USB_COMMAND                                   | 490 |

| 18.16.3  | R_USB_COMMAND_DEV                               | 491 |

| 18.16.4  | R_USB_STATUS                                    | 492 |

| 18.16.5  | R_USB_IRQ_MASK_SET                              | 493 |

| 18.16.6  | R_USB_IRQ_MASK_READ                             | 494 |

| 18.16.7  | R_USB_IRQ_MASK_CLR                              | 495 |

| 18.16.8  | R_USB_IRQ_READ                                  | 496 |

| 18.16.9  | R_USB_IRQ_MASK_SET_DEV                          | 497 |

| 18.16.10 | R_USB_IRQ_MASK_READ_DEV                         | 498 |

| 18.16.11 | R_USB_IRQ_MASK_CLR_DEV                          | 499 |

| 18.16.12 | R_USB_IRQ_READ_DEV                              | 500 |

| 18.16.13 | R_USB_FM_NUMBER                                 | 501 |

| 18.16.14 | R_USB_FM_NUMBER_DEV                             | 502 |

| 18.16.15 | R_USB_FM_INTERVAL                               | 503 |

| 18.16.16 | R_USB_FM_REMAINING                              | 504 |

| 18.16.17 | R_USB_FM_PSTART                                 | 505 |

| 18.16.18 | R_USB_RH_STATUS                                 | 506 |

| 18.16.19 | R_USB_RH_PORT_STATUS_1                          | 507 |

| 18.16.20 | R_USB_RH_PORT_STATUS_2                          | 508 |

| 18.16.21 | R_USB_EPT_INDEX                                 | 509 |

| 18.16.22 | R_USB_EPT_DATA                                  | 510 |

| 18.16.23 | R_USB_EPT_DATA_ISO                              | 511 |

| 18.16.24 | R_USB_EPT_DATA_DEV                              | 512 |

| 18.16.25 | R_USB_EPID_ATTN                                 | 513 |

| 18.16.26 | R_USB_PORT1_DISABLE                             | 514 |

| 18.16.27 | R_USB_PORT2_DISABLE                             | 515 |

| 18.17 MI | MU Registers                                    | 516 |

| 18.17.1  | R_MMU_CONFIG                                    | 516 |

| 18.17.2  | R_MMU_KSEG                                      | 518 |

| 18.17.3  | R_MMU_CTRL                                      | 519 |

| 18.17.4  | R_MMU_ENABLE                                    | 520 |

| 18.17.5  | R_MMU_KBASE_LO                                  | 521 |

| 18.17.6  | R_MMU_KBASE_HI                                  | 522 |

| 18.17.7  | R_MMU_CONTEXT                                   | 523 |

| 18.17.8  | R_MMU_CAUSE                                     | 524 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 525                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 18.17.10 R_TLB_LO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 526                                                                |

| 18.17.11 R_TLB_HI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 527                                                                |

| 18.18 Synchronous Serial Port Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 528                                                                |

| 18.18.1 R_SYNC_SERIAL1_REC_DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 528                                                                |

| 18.18.2 R_SYNC_SERIAL1_REC_WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 529                                                                |

| 18.18.3 R_SYNC_SERIAL1_REC_BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 530                                                                |

| 18.18.4 R_SYNC_SERIAL1_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 531                                                                |

| 18.18.5 R_SYNC_SERIAL1_TR_DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 532                                                                |

| 18.18.6 R_SYNC_SERIAL1_TR_WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 533                                                                |

| 18.18.7 R_SYNC_SERIAL1_TR_BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 534                                                                |

| 18.18.8 R_SYNC_SERIAL1_CTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 535                                                                |

| 18.18.9 R_SYNC_SERIAL3_REC_DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 538                                                                |

| 18.18.10 R_SYNC_SERIAL3_REC_WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 539                                                                |

| 18.18.11 R_SYNC_SERIAL3_REC_BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 540                                                                |

| 18.18.12 R_SYNC_SERIAL3_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 541                                                                |

| 18.18.13 R_SYNC_SERIAL3_TR_DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 542                                                                |

| 18.18.14 R_SYNC_SERIAL3_TR_WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 543                                                                |

| 18.18.15 R_SYNC_SERIAL3_TR_BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 544                                                                |

| 18.18.16 R_SYNC_SERIAL3_CTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

| 18.18.17 R_SYNC_SERIAL_PRESCALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 548                                                                |

| 19 Electrical Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 551                                                                |

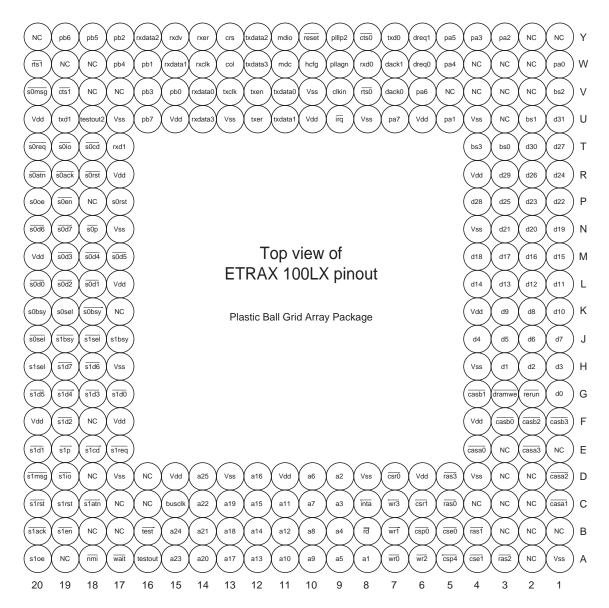

| 19.1 Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

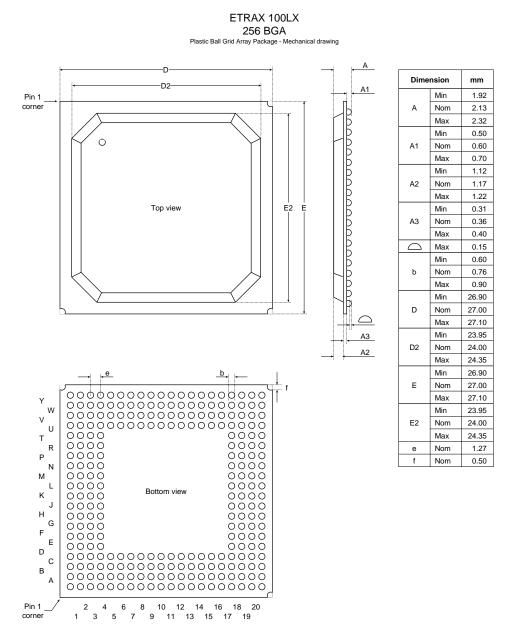

| 19.2 Clock and PLL Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

| 19.3 Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 552                                                                |

| 19.3 Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| 19.4 Bus Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 553                                                                |

| <ul><li>19.4 Bus Interface Signals</li><li>19.5 Logic Analyzer Mode and Test Signals</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 553<br>556                                                         |

| <ul> <li>19.4 Bus Interface Signals</li> <li>19.5 Logic Analyzer Mode and Test Signals</li> <li>19.6 General Port PA Signals</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 553<br>556<br>557                                                  |

| <ul> <li>19.4 Bus Interface Signals</li> <li>19.5 Logic Analyzer Mode and Test Signals</li> <li>19.6 General Port PA Signals</li> <li>19.7 Asynchronous Serial Port 0 Signals</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 553<br>556<br>557                                                  |

| 19.4 Bus Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 553 556 557 558                                                    |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 553 556 557 557 558                                                |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A                                                                                                                                                                                                                                                                                                                                                                                                                              | 553 556 557 558 561                                                |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A                                                                                                                                                                                                                                                                                                                                                                                                                              | 553 556 557 558 561 561                                            |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B                                                                                                                                                                                                                                                                                                                                                                                    | 553 556 557 558 559 561 562                                        |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C                                                                                                                                                                                                                                                                                                                                          | 553 556 557 558 561 562 562                                        |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D                                                                                                                                                                                                                                                                                                | 553 556 557 558 561 562 562                                        |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E                                                                                                                                                                                                                                                      | 553 556 557 558 561 562 563 563                                    |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F                                                                                                                                                                                                            | 553<br>556<br>557<br>558<br>561<br>562<br>562<br>563<br>563        |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F  19.10 Multiplexed Interfaces                                                                                                                                                                              | 553 556 557 558 561 562 563 563 564                                |

| 19.4 Bus Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 553<br>556<br>557<br>558<br>561<br>562<br>562<br>563<br>563<br>564 |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F  19.10 Multiplexed Interfaces  19.10.1 SCSI Ports  19.10.2 ATA                                                                                                                                             | 553 556 557 558 561 562 562 563 563 564 567                        |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F  19.10 Multiplexed Interfaces  19.10.1 SCSI Ports  19.10.2 ATA  19.10.3 Parallel Ports                                                                                                                     | 553 556 557 558 561 562 562 563 564 564 564 565                    |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F  19.10 Multiplexed Interfaces  19.10.1 SCSI Ports  19.10.2 ATA  19.10.3 Parallel Ports  19.10.4 Shared RAM and Shared RAM-W  19.10.5 Asynchronous Serial Ports  19.10.6 Synchronous Serial Ports p1 and p3 | 553 556 557 558 561 562 562 563 564 564 567 570                    |

| 19.4 Bus Interface Signals  19.5 Logic Analyzer Mode and Test Signals  19.6 General Port PA Signals  19.7 Asynchronous Serial Port 0 Signals  19.8 Network Interface Signals  19.9 Multiplexed Signal Groups  19.9.1 Multiplexed I/O Signals - Group A  19.9.2 Multiplexed I/O Signals - Group B  19.9.3 Multiplexed I/O Signals - Group C  19.9.4 Multiplexed I/O Signals - Group D  19.9.5 Multiplexed I/O Signals - Group E  19.9.6 Multiplexed I/O Signals - Group F  19.10 Multiplexed Interfaces  19.10.1 SCSI Ports  19.10.2 ATA  19.10.3 Parallel Ports  19.10.4 Shared RAM and Shared RAM-W  19.10.5 Asynchronous Serial Ports                                             | 553 556 557 558 561 562 562 563 564 564 567 567 572 573            |

## Contents

| 19.10.9   | I2C                                   | 577        |

|-----------|---------------------------------------|------------|

| 19.10.10  | General Port PB                       | 577        |

| 19.11 I/C | O Pin Default Values                  | 578        |

|           | C Electrical Specifications           |            |

|           | Absolute Maximum Ratings              |            |

|           | Recommended Operating Conditions      |            |

|           | Capacitance                           |            |

|           | DC Electrical Characteristics         |            |

| 19.12.5   | Input Buffer Types                    | 580        |

|           | Electrical Specifications             |            |

|           | Conditions                            |            |

| 19.13.2   | SRAM/Flash/Peripheral Timing          | 583        |

|           | Synchronous DRAM                      |            |

| 19.13.4   | Asynchronous DRAM                     | 590        |

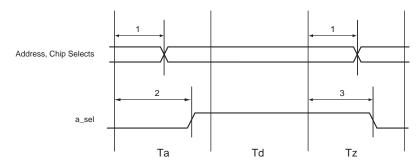

| 19.13.5   | General Bus Interface Timing Diagrams | 594        |

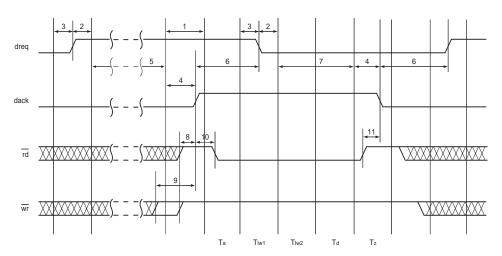

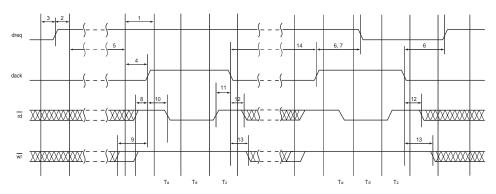

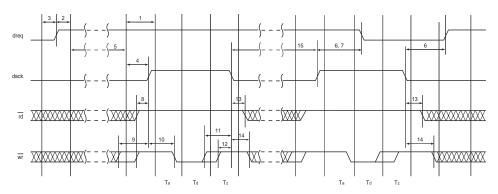

|           | External DMA Timing Diagrams          |            |

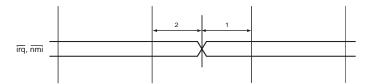

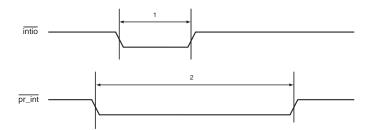

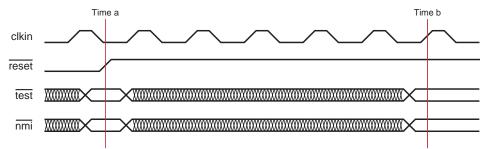

|           | irq and nmi Timing                    |            |

|           | Shared RAM Interface Timing           |            |

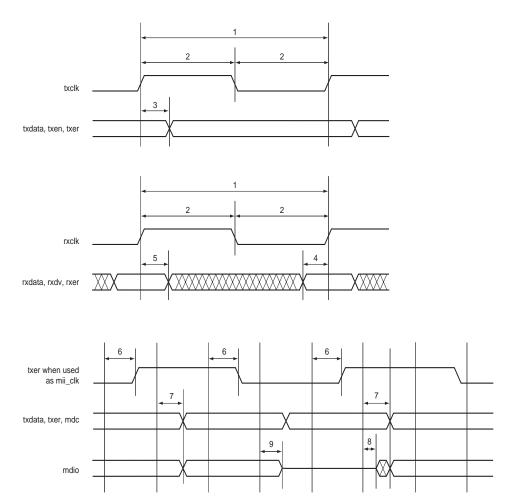

| 19.13.9   | Network Interface Timing              | 604        |

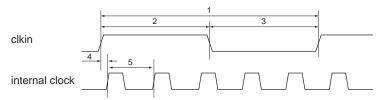

| 19.13.10  | Reset and Clock Timing                | 605        |

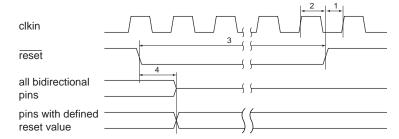

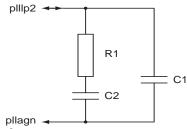

|           | ysical Dimensions                     |            |

| Appendi   | ix A Register Address Index           | <b>309</b> |

|           |                                       | 615        |

|           |                                       |            |

# 1 Introduction

Optimized Network Controller with RISC CPU, Cache and Multiple I/O Ports

### 1.1 Overview

The AXIS ETRAX 100LX is a single-chip integrated circuit designed for embedded network connectivity applications. The ETRAX 100LX improves upon the features available for the AXIS ETRAX 100, including support for Universal Serial Bus 1.1. It is compatible with the widespread ETRAX family, and offers further advances in microprocessor design and performance. The ETRAX 100LX chip incorporates the AXIS CRIS CPU which not only suits all the requirements of a network connectivity product, but also acts as an integrated core especially suited for our system.

The ETRAX 100LX is ideal in executing multi protocol network stacks on one chip. The ETRAX 100LX has a 100 MIPS RISC CPU, 8 kilobyte unified instruction/data cache, high bandwidth DMA controlled I/O ports, and an on-chip Fast Ethernet controller. Its integrated functions, minimal power consumption, and high code density makes it highly suitable for a wide range of embedded applications that require high performance and low system cost.

The ETRAX 100LX programmable bus interface supports both 16-bit and 32-bit data bus widths, and interfaces directly to SDRAM, EDO DRAM, SRAM, EPROM, parallel EEPROM, and FlashPROM.

## 1.2 Features

- High performance 100 MIPS (200 MIPS/W) 32-bit RISC CPU, 112k Dhrystones.

- Designed specifically for running Linux by including an MMU.

- Ethernet controller supports 100Mbit/10Mbit MII (Compatible with IEEE 802.3 and Fast Ethernet standards).

- Four asynchronous serial ports with an internal baudrate programmable from 48 Hz to 6.25 MHz, and an external baudrate up to 3.125 MHz.

- Two synchronous serial ports. Master or Slave synchronous serial mode with a codec clock between 32 kHz and 4.096 MHz.

- Universal Serial Bus 1.1 Host and Device mode operation. Hardware support for dynamic connect/disconnect, suspend/resume and remote wakeup.

- Configuration of up to four EIDE/ATA-2 ports for up to 8 IDE disk drives.

- 16-bit general I/O port. The direction of each bit can be individually controlled.

- Two configurable parallel I/O ports for Centronics, IEEE 1284 byte, ECP, and EPP mode, and Shared RAM interface.

- Optimized for compact code and high speed with configurable 16-bit or 32-bit bus width.

- Bus interface supporting SDRAM, EDO DRAM, SRAM, EPROM, parallel EEPROM, and FlashPROM.

- 8 kilobyte on chip cache memory.

- DMA controlled network and port I/O for high performance

- Excellent C/C++ language support and high code density.

- Configurable bootstrap through network, serial, and parallel ports as well as FlashPROM.

- Low power consumption, 350 mW typically.

- 256-pin PBGA package, 27 x 27 x 2.15 mm.

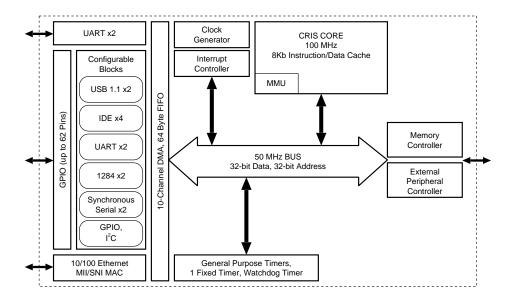

# 1.3 Functional Block Diagram

The CPU in ETRAX 100LX is a RISC CPU with internal cache memory. Data handling is provided by internal DMA within the chip as well as to and from external units. The internal clocks are generated by a PLL clock multiplier that takes its input from an external clock generator. ETRAX 100LX provides internal and external vectorized interrupt.

# 2 RISC CPU

The CPU in ETRAX 100LX is a 32-bit RISC CPU with a 16-bit wide instruction. The CPU complies with the Axis Code Reduced Instruction Set (CRIS) architecture. It runs at a cycle frequency of 100 MHz, giving a peak performance of 100 MIPS. A summary of the CRIS architecture is given below. The CRIS CPU architecture is described in more detail in the "ETRAX 100LX Programmer's Manual".

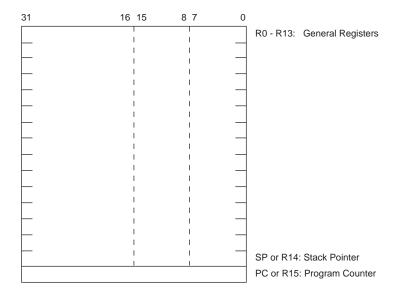

# 2.1 Registers

The processor contains 14 32-bit *General Registers* (R0 - R13), one 32-bit *Stack Pointer* (R14 or SP), and one 32-bit *Program Counter* (R15 or PC).

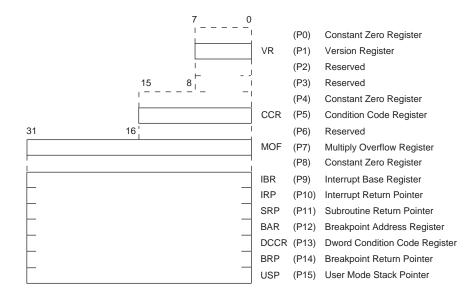

The processor architecture also contains 16 *Special Registers* (P0 - P15), ten of which are implemented. The registers are presented in the figures below:

#### **General Registers:**

Figure 2-1 General Registers

#### **Special Registers:**

Figure 2-2 Special Registers

# 2.2 Flags and Condition Codes

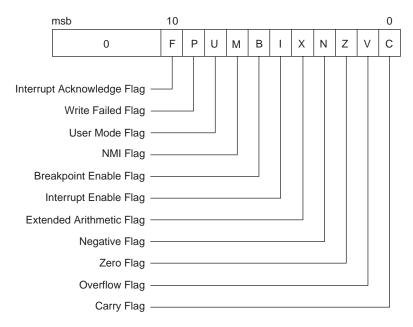

The Condition Code Register (CCR) and its 32-bit extension, the Dword Condition Code Register (DCCR), for the ETRAX 100LX contain eleven different flags. The remaining bits are always zero:

Figure 2-3 The Condition Code Register (CCR)/Dword Condition Code Register (DCCR)

These flags can be tested using one of the 16 *condition codes* specified below:

| Code | Alt | Condition        | Encoding | <b>Boolean Function</b>                                   |

|------|-----|------------------|----------|-----------------------------------------------------------|

| CC   | HS  | Carry Clear      | 0000     | C                                                         |

| CS   | LO  | Carry Set        | 0001     | С                                                         |

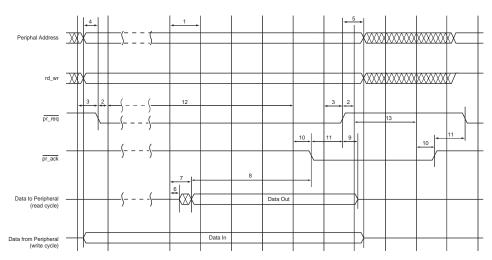

| NE   |     | Not Equal        | 0010     | Z                                                         |